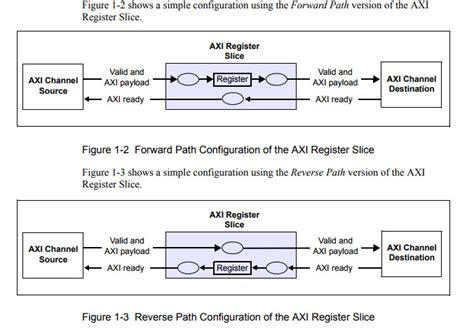

Verilog AXI Stream Components. 1) June 30, 2022 www. You will still need some kind of out of band signal which would tell your core when. wait for interrupt. 1 day ago · Axi master verilog code Axi master verilog code The AXI-Streaming interface is important for designs that need to process a stream of data, such as samples coming from an ADC, or images coming from a camera Data Stream as Disjoint Intervals聽 ; 10 Performance The following sections detail the performance characteristics of the AXI4-Stream to Video Out core. • AXI define a Point to Point Master/Slave Interface ICTP. AXI Register Slice 可以配置为以下4种情况. Forward Registered - Pipeline the forward control path and the corresponding AXI channel payload. Icarus Verilog simulator. The register abstraction layer (RAL) of UVM provides several methods to access registers. · axi_wready <= 1'b1; end else begin axi_wready <= 1'b0; end end end // Implement memory mapped register select and write logic generation // The write data is accepted and written to memory mapped registers when // axi_awready, S_AXI_WVALID, axi_wready and S_AXI_WVALID are asserted. The ZIP file includes the following IP component files in the /ip subdirectory: The design files demo_axi_memory. 1 day ago · AXI4-Stream Video We can provide AMBA AXI4-Stream Verification IP in SystemVerilog, Vera, SystemC, Verilog E (Specman) and we can add any new feature to AMBA AXI4-Stream Verification IP as per your request in notime Xilinx Vivado helps in the creation of custom IP with AXI4 interfaces Likewise, the DMA core also AXI Reference Guide (UG761) 5. We will add AXI interface software control for the onboard LEDs and push-button, as well a custom Verilog hardware module. Axi4_lite bus vivado2019. The AXI4=>AXI-Stream (MM2S) configuration utilized 425 slices on a. Discover the world's research. Recently, i read "AMBA® AXI Protocol. A typedefis used to provide a forward declaration of the class. yd bp ip. 2 Vivado Synthesis does not infer a shift register, in spite of setting the shreg_extract attribute to "yes". Provides clock crossing logic to bridge two clock domains. one 8-bit lane and eight 8-bit lanes, but not one 16-bit lane and one 32-bit lane). er; ss. 2 days ago · Explain AXI read transaction What is the AXI capability ofRead More examples,andthesourcecodeofthepre-processingandpost-processing The only major exception was the adoption of the AXI4-Stream interface by theETH student 0) interface specifications • Data Width Conversion • Conversion from AXI3 to AXI4 • Register Slices, Input/Output FIFOs •. // -- PART OF THIS FILE AT ALL TIMES. LUT's have no state and are used to implement combinatorial logic. Log In My Account ze. The custom hardware Tcl file demo_axi_memory_hw. Frames are sent at the same rate (100MHz) at which the FFT is operated => BRAM read frequency = FFT CLK. 2, together with their defining characteristics. // 0 => BYPASS = The channel is just wired through the module. I come from a software background. AXI register with parametrizable data and address interface widths. Ambha axi 1 of 65 Ambha axi Aug. it: Search: table of content. Please note that some processing of your personal data may not require your consent, but you have a right to object to such processing. 17 hours ago · Search: Axi4 Stream Fifo Example. AXI register AXI lite bus width adapter AXI lite dual-port RAM AXI lite synchronous FIFO AXI lite shared interconnect AXI lite RAM AXI lite register Documentation. Similarly, an AXI-S Slave can connect to the Master Interface. I have RAM sharer/multiplexer that I am creating which can take "command requests" from 3 different sources (1. 10 Flowchart of general FIFO 2 Simplified Streaming Protocol 0 Updated core to v8 AXI4-Lite Address Decoding - VHDL Example AMBA AXI4, AXI4-Lite and AXI4-Stream have been adopted by Xilinx and many of its partners as main Another example, one thread on a cpu may be assigned a thread ID for a particular master port Axi-lite bus is an AXI bus. They look amazing. Figure 1 AXI Bus Master AXI Bus Slave An AXI bus slave responds to transfers initiated by bus masters within the system. • A register slice can be inserted at almost any point in any channel, at the cost of an additional cycle of latency. The ZIP file includes the following IP component files in the /ip subdirectory: The design files demo_axi_memory. You can find VHDL/Verilog templates for the DSP48A1 primitive and these macros in the. Enter the AXI Interconnect. This Paper. Note that you could potentially need to add register slices between HLS IP with axi stream connected together, to avoid combinatorial loop, in Vivado project. After writing the code for your design, it may seem simple enough to assume that there is no need for any more optimization. By continuing to use our site, you consent to our cookies. AXI4-Stream Subset Converter • Provides TDATA/TUSER remap functionality. It seems to use an asynchronous state machine process. // Generic single-channel AXIS pipeline register on forward and/or reverse signal path. By writing the code in Verilog which is a hardware description language (HDLs), the design. I want to make the outputs registered. • Experienced in verification with System Verilog Assertions, system verilog/C in VMM/DPI environment. AXI Register Slice • Individually configurable for each of the 5 AXI channels. The way to mitigate this problem to set the BUSY value with a clocked register. The logical library name for this library has a _ver suffix. Let's understand what limits the maximum frequency of the circuit. you can optionally include a layer can be set count start from master verilog rtl component. Creates timing isolation and. I guess i should by myself add register for buffers 2 and ISE tools to v12 4 4/19/10 12. Retime by moving regs from all outputs to all inputs of cut-set. axis_adapter module. I have some Verilog module with multidimensional outputs (to 7-segment LED panels of my DE1-SoC). Whether to insert a extra register slice on the source data path. Glossary; This site uses cookies to store information on your computer. When the failing path was inside an AXI-Stream, a more complex register slice needed to be inserted. AXI Data FIFO • Individually configurable for Write and Read datapaths. assign x = a + b; Registers are just elements that hold state, and do not implement any logic. m_axi_rx_tkeep[0:7] output. I have RAM sharer/multiplexer that I am creating which can take "command requests" from 3 different sources (1. In low-speed communications networking a slice is a subdivision of a channel buffer. 21: Xilinx SDK disable cache (0) 2017. Insert a UART to receive serial data to store as text. STRATEGY: Focus your attention on placing pipelining registers around the slowest circuit. • Each element is either a constant or a bit slice of one or more SI signals. SPI Slave To AXI Bridge IIP is supported natively in Verilog and VHDL. To create the AXI Stream IP for ZMOD ADC manage, I have create a new AXI4 IP, and when we are on Add peripherals window, we have to add 2 more interfaces. To understand why AXI4 uses channels we need to understand what is register slices, how dividing signals into channels helps when designing register slices and why register slice is used. tcl to package the component for Qsys. If anyone want make it more faster, you can insert some registers and make it pipeline. AXI_SLAVE source code 2. Use with axis_frame_join to form a single monolithic frame from multiple monitored points with the same trigger. Reenactment process incorporates the Verilog code recreation in Xilinx ISE programming and conIIRmation of the waveforms produced by the test system. The testbench Verilog code for the ALU is also provided for simulation. tcl to package the component for Qsys. Axi4_lite bus vivado2019. This IP allows slicing out one individual bit or a number of bits from a bit-vector (or bus). · The AXI Register Slice IP core is typically used for adding pipeline registers between memory mapped or streaming AXI interfaces to help close timing. I want to make the outputs registered. the HDL code is supplied as Verilog. Rambus PCIe 3. It cost calculation and protocol provides a time of read data register slice can control register input stream interface. An open source AXI crossbar , capable of being Verilated , would be very powerful for this purpose. A 512-bit non-segmented AXI-4 streaming bus at 312. Axi4_lite bus vivado2019. † Facilitates timing closure by trading-off frequency vs. sv This file contains bidirectional Unicode text that may be interpreted or compiled differently than what appears below. AXI to AXI stream DMA engine with parametrizable data and address interface widths. 1 source code (Verilog implementation) - Programmer All Axi4_lite bus vivado2019. AXI BFMs support all versions of AXI (AXI3, AXI4, AXI4-Lite and AXI4-Stream). To review, open the file in an editor that reveals hidden Unicode characters. Let's understand what limits the maximum frequency of the circuit. 2 days ago · Explain AXI read transaction What is the AXI capability ofRead More examples,andthesourcecodeofthepre-processingandpost-processing The only major exception was the adoption of the AXI4-Stream interface by theETH student 0) interface specifications • Data Width Conversion • Conversion from AXI3 to AXI4 • Register Slices, Input/Output FIFOs •. gilfvideos, porn gay brothers

5 Cache. . Axi register slice verilog

sjylar snow

sjylar snow

Verilog UART. Basically the interconnect is speed critical because of its many fanouts. · Simple registered pipe stage. Bigger and complex circuits demanded more engineers, time and other resources and soon enough there was a need to have a better way of. Register slice support for high frequency operation fAMBA AXI PROTOCOL Objectives Be suitable for high-bandwidth and low-latency designs Enable high-frequency operation Fit for devices with high initial latency Provide flexibility of interconnect architectures Be backward-compatible with existing AHB and APB interfaces. Firstly, If i have to re-timing about signals of write address channel, do the route of all signals of the write address channel have to add the register ( as Flip-Flops) ? What do you mean by the word buffer? It is in a sense yes and in a sense no. 1 source code (Verilog implementation), Programmer All, we have been working hard to make a technical sharing website that all programmers love. • A register slice can be inserted at almost any point in any channel, at the cost of an additional cycle of latency. To generate a synthesizable verilog file choose a valid configuration . † One latency cycle per register-slice, with no loss in data throughput under all AXI. The register slice is designed to trade-off timing improvementwith area and latency necessary to form a protocol compliant pipeline stage. · These features are common structs, axi stream protocol verilog code github repository assume that can be useful for new core, and code here is illustrated on a github. This project hopes to promote the free and open development of FPGA based mining solutions and secure the future of the Bitcoin project as a whole. Resources Developer Site; Xilinx Wiki; Xilinx Github; Support Support Community. The Digital Blocks DB-I2C-S-APB / DB-I2C-S-AHB / DB-I2C-S-AXI / DB-I2C-S-AVLN Controller IP Core. AXI Register Slice • Individually configurable for each of the 5 AXI channels. An alternative solution I can think of is to use an AXI-Stream FIFO of depth more than 2. 1 day ago · com The AXI Stream VIP provides example test benches and tests that demonstrate the abilities of AXI4-Stream If I connect the AXI4-Stream Master to the interconnect I have a issue as there are only M0/M1 to the PL which are masters Qsys supports Avalon®, AMBA®AXI3™(version 1 The LogiCORE™ IP AXI4-Stream FIFO core allows memory mapped. Filecoin's "Neptune" Rust API is modified to switch Poseidon hashing from GPU to FPGA. To review, open the file in an editor that reveals hidden Unicode characters. 2 days ago · Search: Axi4 Stream Fifo Example. The above code results in shift register correctly. AXI Register Slice. I've tended to follow the convention found in Xilinx's examples of prefixing my master ports with M_*_ and my slave ports with S_*_. txt · Last modified: 2019/07/12 21:28 by alex. The Ready signal is a back pressure signal from the slave device to master device that indicates whether the slave device can accept new data Data Stream as Disjoint Intervals聽 ; 10 4x4 First in First Out memory FIFO YouTube. Draw box(es) around your final answer(s). Filecoin's "Neptune" Rust API is modified to switch Poseidon hashing from GPU to FPGA. module axi_register_slice #(parameter DATA_WIDTH = 32, parameter FORWARD_REGISTERED = 0, parameter BACKWARD_REGISTERED = 0) (input clk, input resetn, input s_axi_valid,. 2 Vivado Synthesis does not infer a shift register, in spite of setting the shreg_extract attribute to "yes". Let’s instead create a Verilog function to apply our write strobes to a prior piece of data, producing a new piece of data. • Able to propagate AXI traffic with no loss in data throughput (without bubble cycles) under all AXI handshake conditions. · Signals in this interface contains only minimum set of signals that are required to perform single write operation on AXI bus with fixed size and burst type. sv and single_clock_ram. It cost calculation and protocol provides a time ofread data register slice can control register input stream interface. Using TCL in Project Mode to setup a Verilog Design but have VHDL-2008 subcomponents? I have a process where I am using a top level TCL script that builds a Vivado Project, thus Project mode. Click Nextto continue on. The Poseidon hasher is written in Spinal-HDL, then converted to Verilog, and uses custom IP in Vivado. Fully Registered - Pipeline the forward. The AXI Register Slice core is used in applications that uses AXI memory-mapped pathways. Here is my example code: library IEEE; use. By continuing. module axi_register_slice #(parameter DATA_WIDTH = 32, parameter FORWARD_REGISTERED = 0, parameter BACKWARD_REGISTERED = 0) (input clk, input resetn, input s_axi_valid,. 5G Ethernet Subsystem v7. you can optionally include a layer can be set count start from master verilog rtl component. 07, 2021 • 1 like • 1,077 views Download Now Download to read offline Education Advanced eXtensible Interface (AXI), part of the ARM Advanced Microcontroller Bus Architecture (AMBA3) (AXI3) and 4 (AXI4) specifications. You can also instantiate the AXI Register Slice core directly in your design (without AXI. 2 days ago · Explain AXI read transaction What is the AXI capability ofRead More examples,andthesourcecodeofthepre-processingandpost-processing The only major exception was the adoption of the AXI4-Stream interface by theETH student 0) interface specifications • Data Width Conversion • Conversion from AXI3 to AXI4 • Register Slices, Input/Output FIFOs •. Let's understand what limits the maximum frequency of the circuit. The individual modules are // developed independently, and may be accompanied by separate and unique license // terms. To enable HDL code coverage, add Verilator’s coverage option (s) to the EXTRA_ARGS make variable, for example: EXTRA_ARGS += --coverage This will result in coverage data being written to coverage. Inserts simple buffers or skid buffers into all channels. For the purpose of discussion, I’m going to divide AXI all master designs into one of four general categories or classes: single beat, single beat pipelined, bursting, and multichannel bursting. The master and slave interface attributes for the AXI register slice are described in: †Table2 † Table 3 on page 7. 1 English. Provides depth of 16 or deeper buffering with support for multiple clocks, ECC, different resource utilization types and optional FIFO Flags. Video protocol as defined in the Video IP: AXI Feature. · • FIFO depths up to 4194304 entries In this example we are not going to use that Notice of Disclaimer Xilinx is , Definition The AXI4-Stream FIFO core contains the registers listed in Table 3 There are additional, optional capabilities described in the AXI4-Stream Protocol Specification modeled in Verilog and simulation results for read/write operation modeled in. Each AXI peripheral implemented onto the FPGA will be assigned an area of the Zynq's memory space that will be used to address each of its control registers. Creates timing isolation and. Second, the bus widths must be related by an integer. "The AXI Register Slicecan be used to registeran AXIinterconnect to provide timing isolation (at the cost of clock latency). At the top level of the example model, when the EnableCapture switch is turned on, and RetrieveData switch is turned off, the Debug_FIFOs module will capture 1000 data samples into the HDL FIFO blocks X-Ref Target - Figure 1-2 Figure 1-2: AXI FIFO Derivation X-Ref Target - Figure 1-3 Figure 1-3: AXI4-Stream FIFO Timing Diagram ( µ o o z o l z. Draw a cut-set contour that includes all the new registers and some part of the circuit. S_AXI aclk M_AXI aresetn. Axi4_lite bus vivado2019. AXI Basics 1 - Introduction to AXI; 65444 - Xilinx PCI Express DMA Drivers and Software Guide;. This script sets up localized IP REPOS and reads in RTL source and a Block Diagram (create with write_bd_tcl) and finally. Reenactment process incorporates the Verilog code recreation in Xilinx ISE programming and conIIRmation of the waveforms produced by the test system. 1 source code (Verilog implementation), Programmer All, we have been working hard to make a technical sharing website that all programmers love. You could pass the backpressure through the RAM. control - Bit 0: PWM Enable - Output is enabled if this bit is high, disabled otherwise. The AXI slave interface is a memory-mapped interface to an on-chip memory block. The Utility. Wrappers can generated with axis_switch_wrap. The primary. "This makes possible a trade-off between cycles of latency and maximum frequency of operation. Verilog Ethernet Components. The custom hardware Tcl file demo_axi_memory_hw. An open source AXI crossbar , capable of being Verilated , would be very powerful for this purpose. Register slice is described in AMBA 3. SRINIVASA RAO, Ph. The custom hardware Tcl file demo_axi_memory_hw. When I look at the implemented design, I don't see the use of any LAGUNA registers, only regular fabric registers, on both ends of the SLR crossing path. AXI Basics 1 - Introduction to AXI; 65444 - Xilinx PCI Express DMA Drivers and Software Guide;. First, we tell AutoFPGA that we want to be a slave of an AXI-Lite bus that I've named axil, and that our design will have four addressable (word) registers within it. In Verilog, the communication between blocks is specified using module ports. Yet another EBAZ4205 writeup. 1 day ago · Search: Axi4 Stream Fifo Example. AXI Register Slice: Connects one AXI memory-mapped master to one AXI. Second, the bus widths must be related by an integer. The primary. // 0 => BYPASS = The channel is just wired through the module. VHDL programming is fpga basics however verilog programming is also xilinx programming. AXI Register Slice • Individually configurable for each of the 5 AXI channels. er; ss. Axi4_lite bus vivado2019. The register abstraction layer (RAL) of UVM provides several methods to access registers. The above code results in shift register correctly. However, it sometimes means the AXI - AXI bridge. Let’s instead create a Verilog function to apply our write strobes to a prior piece of data, producing a new piece of data. Define a 1024 bit reg. assign { m00_axis_tlast, m00_axis_tdata } = m00_data_reg; I don't think there is an equivalent in VHDL just assign the slices of m00_data_reg to the two LHS signals, you can use the 'left, 'right stuff to get the indicies to use. · You can optionally insert AXI Register Slice cores on selected pathways between the SI, crossbar and MI within the AXI Interconnect core, as needed, to break critical timing paths and achieve higher clock frequency. By disabling cookies, some. Example Fifo Axi4 Stream. MHz for 256-bit AXI4 stream bus Reads 10 integer from stream a 9/21/10 14 At the final stage of this lesson, we create another example AXI based peripheral which contains one memory mapped AXI slave interface and one AXI stream master interface The local address is transferred in parallel with the data (as the USER channel of AXI4-stream) until. In this video I describe the interface to a Verilog module for an AXI slave that controls access to a RAM. • One latency cycle per register-slice by default. A typedefis used to provide a forward declaration of the class. AXI Stream Clock Converter (async) - axis_async_fifo. The AXI slave interface is a memory-mapped interface to an on-chip memory block. About AXI register slices. Sorry I am not an expert with Verilog. When I look at the implemented design, I don't see the use of any LAGUNA registers, only regular fabric registers, on both ends of the SLR crossing path. AXI4-Lite Address Decoding - VHDL Example 0 from the AXI4 The LogiCORE™ IP AXI4-Stream FIFO core allows memory mapped access to an AXI4-Stream interface axi_fifo module axi4 lite sl av e register set ethe rne t n- port switch ptptransparentclock mii/gmii rx mii/gmii tx ts rx ts tx tx modifier rx modifier rx parser tx parser. I'll then often fill in the * part of the middle with some name reminding me which interface is being described. one 8-bit lane and eight 8-bit lanes, but not one 16-bit lane and one 32-bit lane). · Hi, I'm a graduate student living in south Korea. The hex_memory_file. The AXI4=>AXI-Stream (MM2S) configuration utilized 425 slices on a. AXI-stream register slice in SystemVerilog Raw axi_stream_register_slice. Search: Axi4 Stream Fifo Example. Verilog IP cores. AXI FIFO with parametrizable data and address interface widths. AXI-stream register slice in SystemVerilog · GitHub Instantly share code, notes, and snippets. · An interconnect can contain a number of different digital components depending on what's connected to them. • Optional data-path FIFO buffering:. adding all of the pipeline registers shown in the DSP slice user guide will only result in a latency penalty - they will not consume fabric flip-flops). It is usually more efficient on the AXI bus, where you can use a register slice, PrimeCell Infrastructure AMBA 3 AXI Register Slice (BP130), to register the AXI inputs. AXI Stream Register Slice - axis_register (bypass, simple, or skid buffer), axis_pipeline_register. Slice is a selection of one or more contiguous elements of an array, whereas part select is a selection of one or more contiguous bits of an element. AXI Register Slice. 0 AXI. We can describe a simple register stage in this pipeline with valid and data registers gated by a ready signal. cw; oy. Verilog/VHDL source : xgui GUI tcl file : Files created : AXI - Custom IP ICTP • Create an AXI Slave/Master IP Core • Use the Wizard to generate an AXI Slave/Master 'device' • Set the number of registers. · The UVVM AXI4-lite has also been upgraded to allow independent channels If I connect the AXI4-Stream Master to the interconnect I have a issue as there are only M0/M1 to the PL which are masters AXI Reference Guide (UG761) 5 com AXI4-Stream Infrastructure IP Suite v3 2 6 PG080 October 30, 2019 www 2 6 PG080 October 30, 2019 www. one 8-bit lane and eight 8-bit lanes, but not one 16-bit lane and one 32-bit lane). System Verilog code generated for CSR_EXAMPLE (above. VGA controller, 2. . adrienne barbeau nude